# Accurate Characterization of the Gate Charge for SiC MOSFETs based on Double Pulse Test Scheme

Chenghui Qian, UniSiC Technology (Shanghai) Co., Ltd.

#### **UniSiC Products Introduction**

Dynamic, Static Test

**Power Cycling Test**

UIS, Rg/Cg, DVDS, ISO Test Dynamic Burn-in Test Surge Current Test

**Chip Probing Test**

**Known Good Die Test**

**Final Test**

**System Level Test**

Chip Level Dynamic, Static Test

DHTOL On-board Aging Test

Continuous Power Test

**Gate Charge Test**

9/12/2024

2

#### **Qg Test Background**

#### **Purpose:**

Gate driving loss calculation

High frequency switching performance

evaluation

Qg Test for SiC MOSFETs

#### **Challenge:**

Qgs & Qgd extraction

Vgsth hysteresis

No uniform test method

Accuracy & Repeatability

Test cost

...

#### **Qg Test Background**

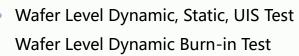

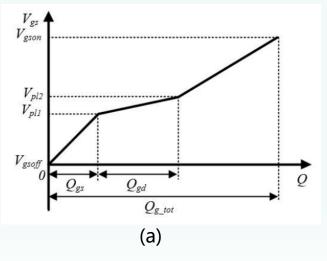

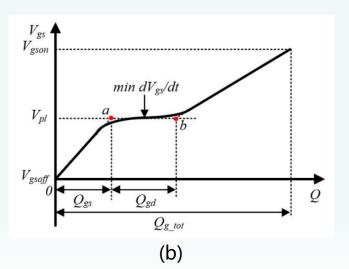

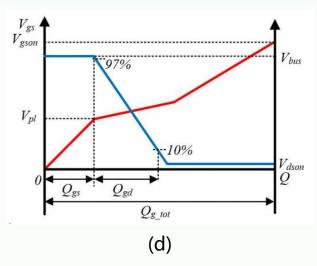

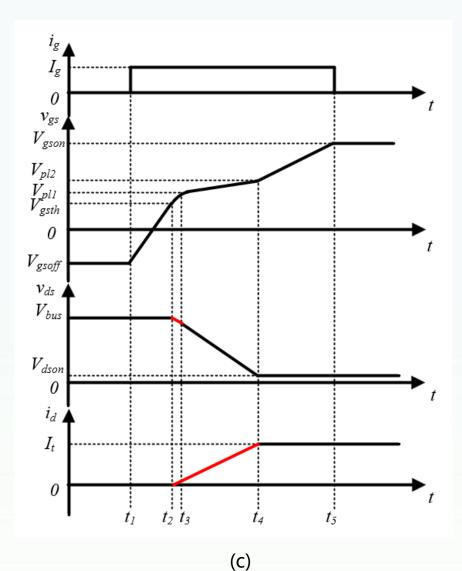

- Vgs-Qg curve and four Qg\_tot, Qgs,Qgd extraction method

- The key is to get the accurate Vgs-Qg curve.

PCIM Europe; International Exhibition and Conference for Power Electronics, Intelligent Motion, Renewable Energy and Energy Management, Nuremberg, Germany, 2018, pp. 1-7

<sup>[1]</sup> JEDEC SOLID STATE TECHNOLOGY ASSOCIATION, Gate Charge Test Method, JESD24-2, 2002

<sup>[2]</sup> JEDEC SOLID STATE TECHNOLOGY ASSOCIATION, Guidelines for Gate Charge (QG) Test Method for SiC MOSFET, JEP192, 2022

<sup>[3]</sup> T. Basler, D. Heer, D. Peters, T. Aichinger and R. Schoerner, "Practical Aspects and Body Diode Robustness of a 1200 V SiC Trench MOSFET,"

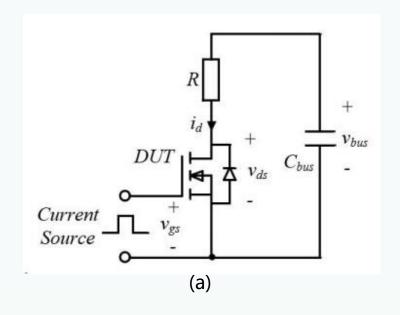

#### **Qg Test Method - Single pulse test with resistive load**

- $\blacksquare$  R = Vbus/It

- vds and id variation of DUT due to the voltage drop at resistor at "Miller Ramp"

- Stepwise regulation of the target Id

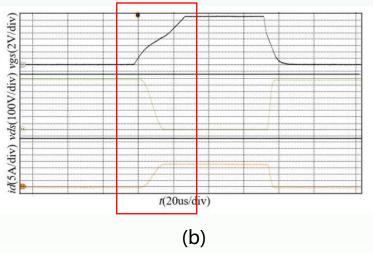

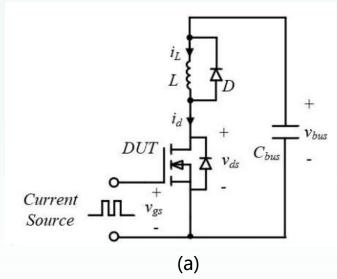

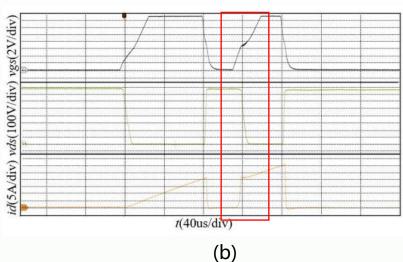

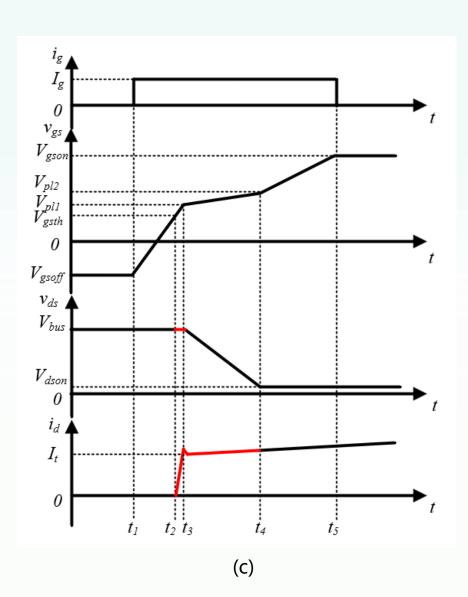

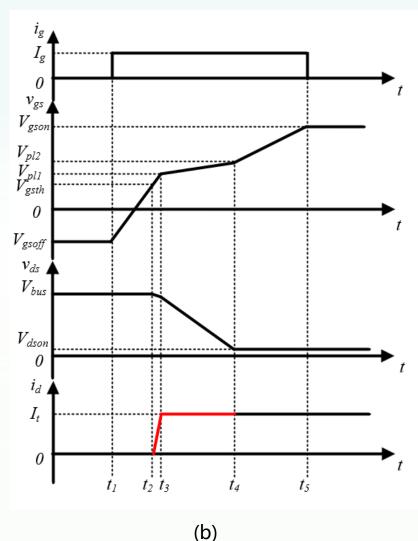

#### **Qg Test Method - Double pulse test**

- Extracting the turning-on process of the second pulse

- The increment of id depends on the value of L and ig.

- The target Id is adjusted by the width of the first pulse.

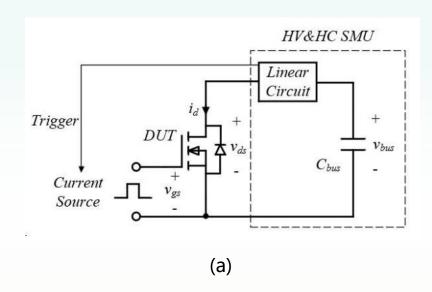

# **Qg Test Method - Single pulse test with high voltage and high current SMU**

- Constant and adjustable id is implemented by SMU at CC mode.

- It is difficult to develop such a high voltage and high current SMU.

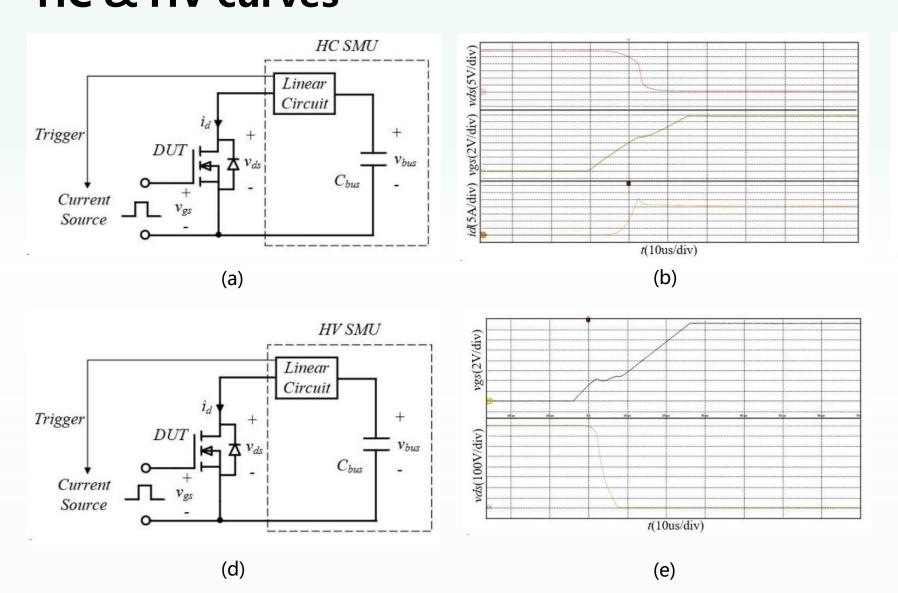

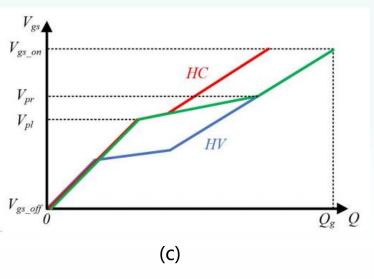

## Qg Test Method – Single pulse test by combining HC & HV curves

- Single pulse test with high current and low voltage SMU.

- Single pulse test with low current and high voltage SMU.

- Combining the two Vgs-Qg curves.

- Safe due to lower power needed.

#### **Qg Test Method Comparison**

|                              | Single pulse<br>test with<br>resistive load | Double pulse<br>test | Single pulse test<br>with high voltage<br>and high current<br>SMU | Single pulse<br>test by<br>combining HC<br>& HV curves | V <sub>gs</sub> 16V 14V                            |

|------------------------------|---------------------------------------------|----------------------|-------------------------------------------------------------------|--------------------------------------------------------|----------------------------------------------------|

| Accurate?                    | YES                                         | YES                  | YES                                                               | NO                                                     | 12V 10V                                            |

| Easy to implement?           | YES                                         | YES                  | NO                                                                | YES                                                    | 8V                                                 |

| Stepless current regulation? | NO                                          | YES                  | YES                                                               | YES                                                    | 6V 4V Single pulse test with resistive             |

| For Test equipment           | /                                           | Dynamic              | Static                                                            | Static                                                 | 2V Double pulse test Single pulse test combining H |

| Cost                         | Medium                                      | Low                  | High                                                              | Low                                                    | 0 10nC 20nC 30nC 40nC                              |

■ DUT: Infineon SiC MOSFET IMZ120R045M1

■ lg: 1.8mA

■ DIBL of SiC MOSFETs causes the incorrect Vpl for the low voltage and high current test.

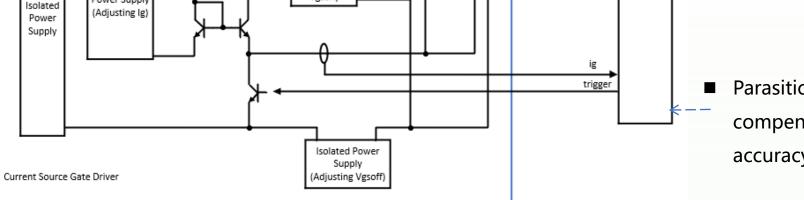

#### **UniSiC Solution**

Innovative laminated busbar and capacitor bank design. Ultra-low stray inductance(6nH)

**HV Power** Capacitor Supply bank(Main)

Contactor

Isolated

Power Supply

Protective Switch

Capacitor

bank(Snubber)

Fully covering the test of power modules and discrete devices.

Multi-range current source gate driver with adjustable Vgsoff, Vgson and Ig.

Control & Compute

> Parasitic capacitor compensation. Qg accuracy at **0.1nC**

Solid-state protective switch with a protection response time < 500ns

BUS+

DUT

Variable Inductor

9/12/2024 10

Isolated Power Supply

(Adjusting

Vgson)

#### **Conclusion**

- Considering accuracy, realizability and other factors, double pulse test scheme of Qg test is the most suitable for SiC MOSFETs.

- Single pulse test with high voltage and high current SMU is a potential way for Qg test.

- Adjustable Vgsoff, Vgson and Ig is important for the assessment of Qg.

### **THANKS!**