pcim ASIA

A 150 & 200mm engineered substrate increasing SiC power device current density up to 30%

<u>Gonzalo PICUN</u>, Eric Guiot, Frédéric Allibert, Alexis Drouin, Walter Schwarzenbach, Soitec - France Jürgen Leib, Tom Becker, Oleg Rusch, Fraunhofer IISB -Germany

- 1. Introduction to SiC engineered semiconductor substrate technology

- 2. SiC engineered substrate characterization

- 3. Lifecycle analysis and process simplification

- 4. Device results

- 5. Takeaways and next steps

## 1. Introduction to SiC engineered semiconductor substrate technology

- 2. SiC engineered substrate characterization

- 3. Lifecycle analysis and process simplification

- 4. Device results

- 5. Takeaways and next steps

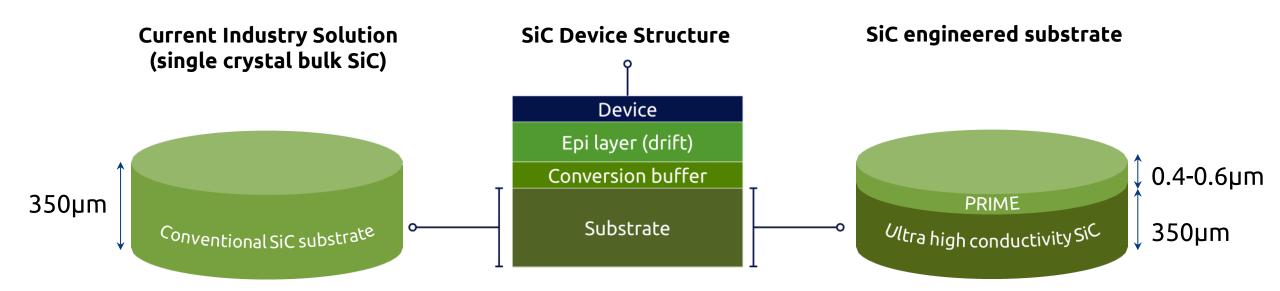

SiC Engineered Substrate: optimum design for Performance & Value

## A unique value proposition

- Smaller size / Higher current density

- Higher manufacturing yield

- Simpler & cheaper manufacturing process

- Improved Power Cycling robustness

- Bipolar Degradation ruggedness

- Fastest path to 200mm transition

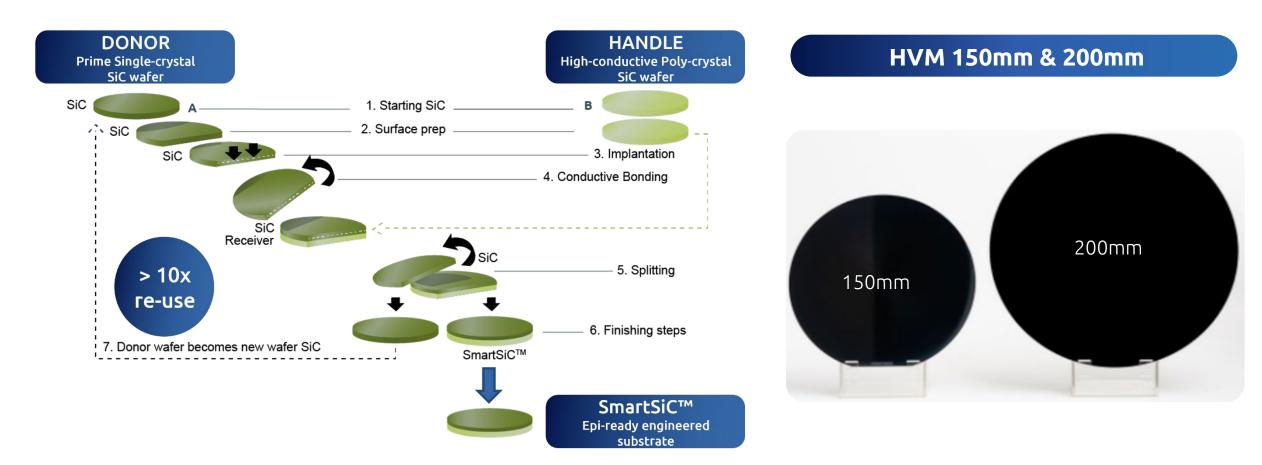

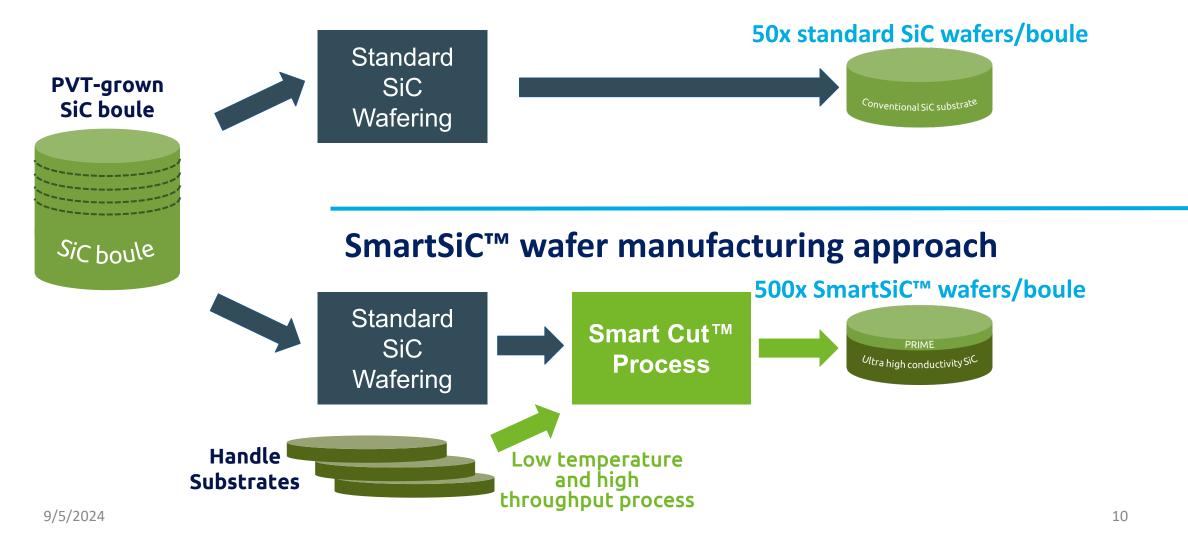

## SmartSiC<sup>™</sup>: Smart Cut<sup>™</sup> Process Adapted to SiC

## Leveraging Soitec's 30-year High Volume Manufacturing Expertise

9/5/2024

- 1. Introduction to SiC engineered semiconductor substrate technology

- 2. SiC engineered substrate characterization

- 3. Lifecycle analysis and process simplification

- 4. Device results

- 5. Takeaways and next steps

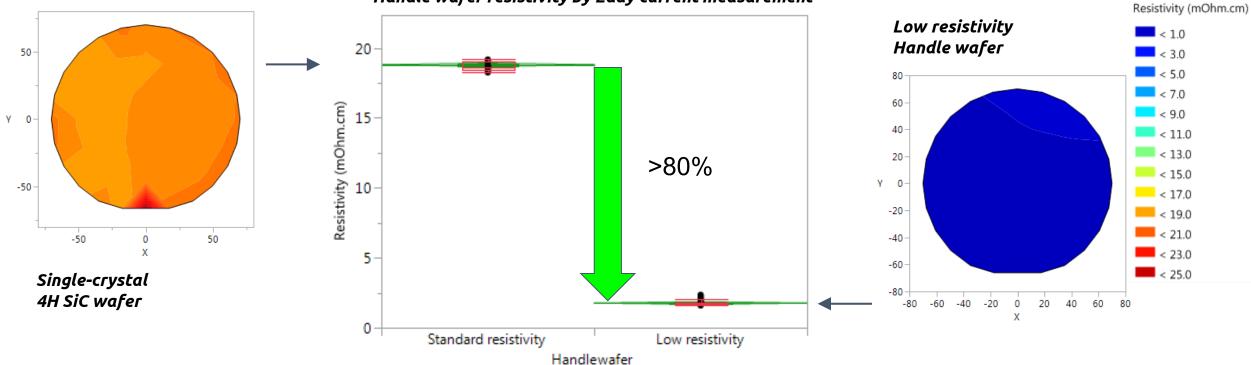

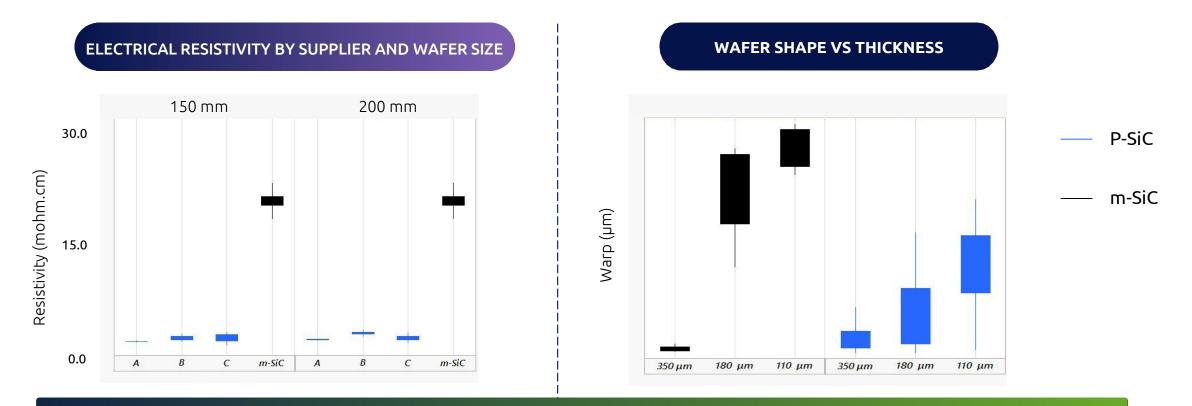

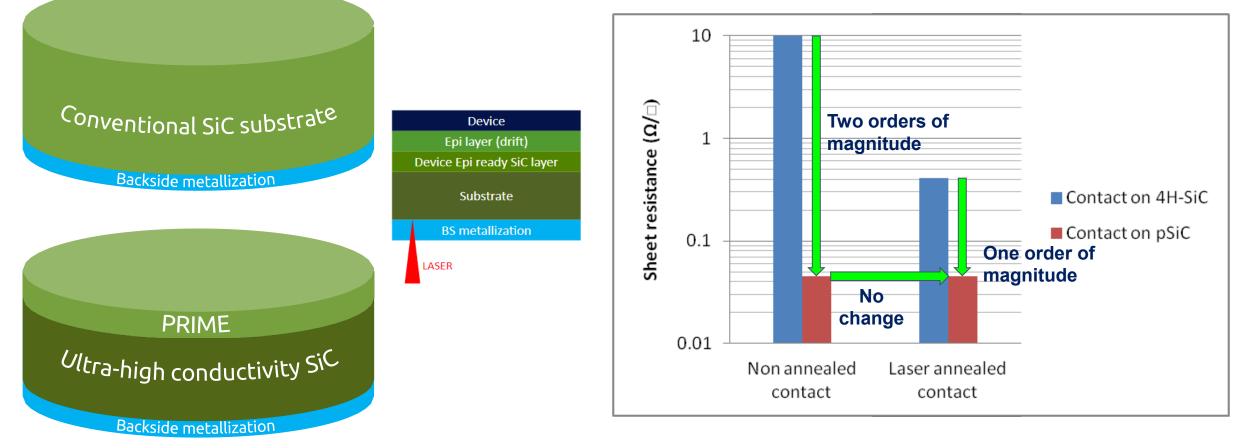

## Polycrystalline SiC: electrical transport properties

#### Handle wafer resistivity by Eddy current measurement

## Substrate resistivity decreased by one order of magnitude

## Polycrystalline SiC: scalable and stable supply chain

- Tight control of electrical resistivity and wafer shape

- Easy scalability from 150 & 200 mm wafers size (cost, performance, volume)

## **Currently in mass production for EV market**

- 1. Introduction to SiC engineered semiconductor substrate technology

- 2. SiC engineered substrate characterization

- 3. Lifecycle analysis and process simplification

- 4. Device results

- 5. Takeaways and next steps

## SiC engineered substrate: optimum reuse of energy intensive mSiC

## Standard SiC wafer manufacturing approach

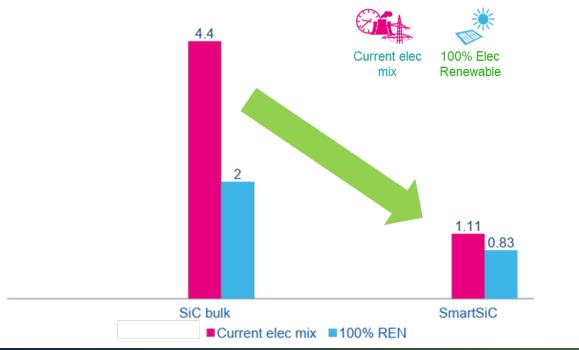

## SiC engineered substrate: reduced CO<sub>2</sub> footprint SiC

g CO2eq / mm<sup>2</sup>

- Carbon emissions for wafers production following a life cycle analysis protocol

- Normalized results per mm<sup>2</sup> based on current and future electrical mix, and manufacturing data

## **Divide by 4 the CO<sub>2</sub> emissions to manufacture SiC wafers**

#### pcim ASIA

## SiC engineered substrate: No Need for Backside Laser Annealing

#### **Ohmic contact without backside laser annealing**

## Higher Yield / Less CAPEX & OPEX

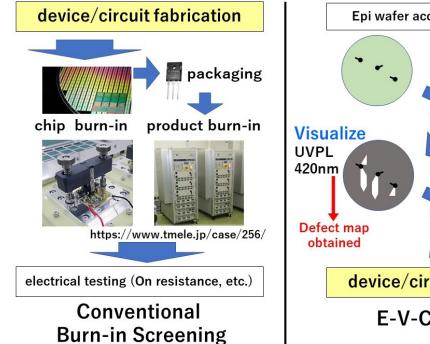

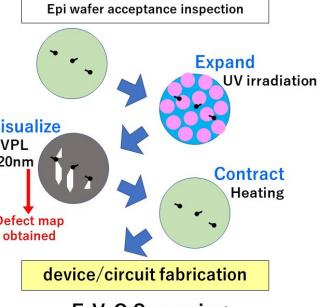

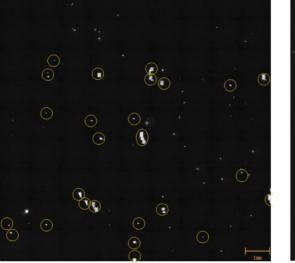

## BPD stressing through UV illumination

ITES Co., Ltd.

**E-V-C Screening**

bulk SiC+10µm drift epi

SmartSiC<sup>™</sup>+10µm drift epi

## SiC engineered substrates are intrinsically robust against bipolar degradation

9/5/2024

- 1. Introduction to SiC engineered semiconductor substrate technology

- 2. SiC engineered substrate characterization

- 3. Lifecycle analysis and process simplification

- 4. Device results

- 5. Takeaways and next steps

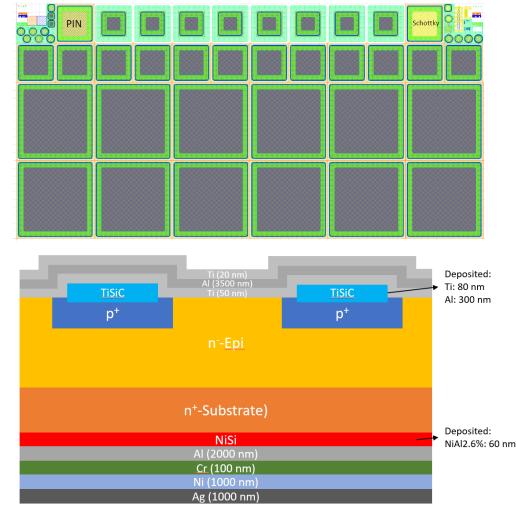

## Design and experimental conditions of SiC diodes

#### Multi project diode mask:

- JBS: 340x340µm → 0.2 Amp

- PIN: 1.6x1.6mm

- MPS: 1.6x1.6mm → 4 Amp

- → 9 Amp MPS: 2.5x2.5mm

### **Process details:**

- Drift layer epitaxy done with Aixtron G5 reactor

- Drift thickness: 11µm

- Drift doping: 1e<sup>16</sup>.cm<sup>-3</sup>

- P+ implanted regions:

- Depth: 500 nm

- Width: 2.5 μm

- Die thickness: 340µm (10µm grinding)

- Back side ohmic contact:

- Laser annealing for 4H-SiC

- No laser annealing for SiC engineered substrate Ο

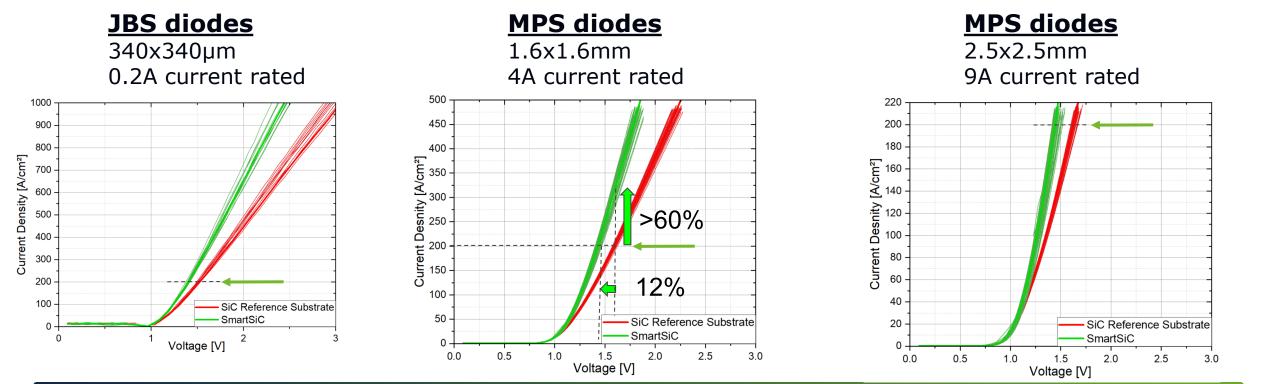

## Diodes on Engineered Substrates: forward characteristics

- 12% gain in V<sub>F</sub> (@ 200 Amp/cm<sup>2</sup>) for all diodes

- 60% gain in forward current at constant forward voltage

## In line with engineered substrate characteristics

**ASIA**

#### pcim ASIA

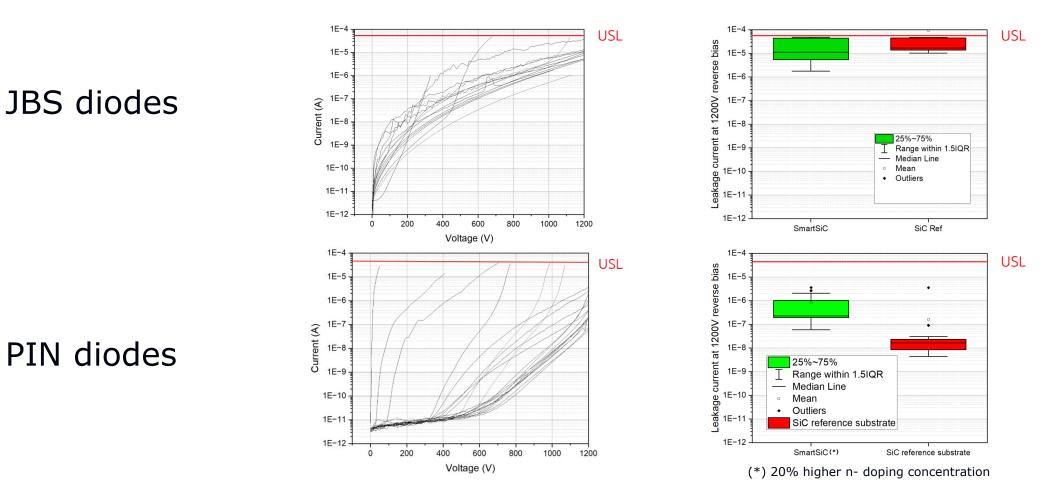

### Diodes on Engineered Substrates: reverse characteristics

### **Reverse current within device specification limits**

SiC Engineered Substrate: unleashing performance and productivity

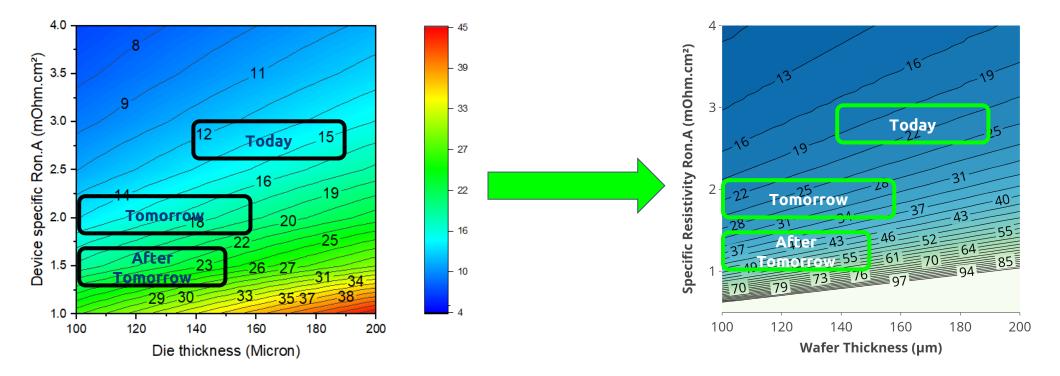

#### Percentage of Ron.A gain vs. initial Ron.A and wafer thickness

### Percentage of Addtl. Good Die/Wfr vs. initial Ron.A and wafer thickness

### **Increasing manufacturing capacity at no additional CAPEX**

# pcim

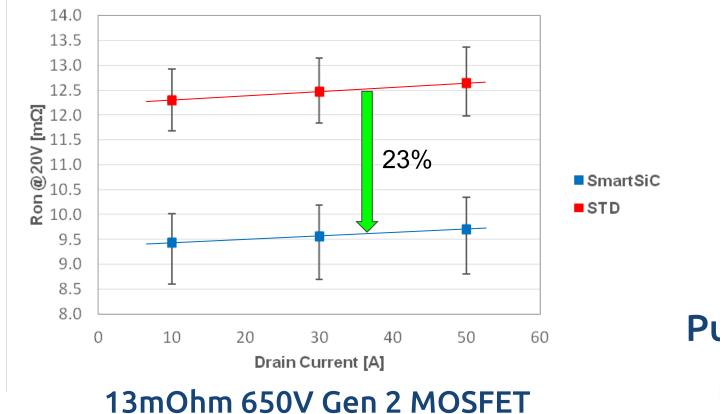

## Results from an HVM SiC MOSFET: gain equivalent to a generation leap

## TRANSFORM

Funded by the Key Digital Technologies Joint Undertaking under Grant Agreement No. 101007237

## Published on June 1st, 2024, in: Bodo S Power Systems®

## 23% Ron reduction, without any mask nor process step change

- 1. Introduction to SiC engineered semiconductor substrate technology

- 2. SiC engineered substrate characterization

- 3. Lifecycle analysis and process simplification

- 4. Device results

- 5. Takeaways and next steps

## Takeaways and Next Steps

- SiC engineered substrates, based on the Smart Cut™ process, provide optimized characteristics from:

- Single-crystal 4H-SiC high-quality top layer

- Ultra-high conductivity polycrystalline SiC base wafer

- SiC engineered substrates offer unprecedented advantages

- Minimal substrate contribution to the total device resistance

- CO<sub>2</sub> footprint reduced by a factor of 4 with respect to a standard SiC wafer

- Capability to skip backside laser annealing, reducing CAPEX and OPEX

- Ruggedness to bipolar degradation

- Demonstrated improved performance for diodes and transistors equivalent to a generation leap

- Optimizing manufacturing capacity at no additional CAPEX

- Next steps (submitted for ICSCRM 2024):

- Planar and trench MOSFETs: conduction and switching losses

- Reliability assessment: current surge, short circuit

# 感谢您的关注 THANK YOU FOR YOUR ATTENTION

pcim

ASIA

## **Gonzalo PICUN**

WBG Business Development Manager gonzalo.picun@soitec.com