# pcim **ASIA**

# An Automatic Optimization Algorithm of SiC MOSFET Power **Cycling Test parameters Based on the Device Thermal Networks**

## Hao Jin<sup>1,2</sup>, Jin Zhang<sup>1</sup>, Xinyu Zou<sup>1,2</sup>, Yao Yan<sup>1,2</sup> <sup>1</sup> Institute of Electrical Engineering of the Chinese Academy of Sciences, China <sup>2</sup> University of Chinese Academy of Sciences, China

## **1.Introduction**

Power device is the key part of power electronic system and is widely used in electric power transmission, highspeed rail, electric car and industrial control, etc. The third generation semiconductor devices represented by SiC have gradually become the competitive focus of relative industry for their higher performance. Power cycling (PC) test, as the most important test to assess the reliability of power devices, through the external current state of on and off to simulate the device in the actual working conditions of the switching process, to the chip in the device as a heat source, on the basis of not changing the failure mechanism to accelerate the aging.

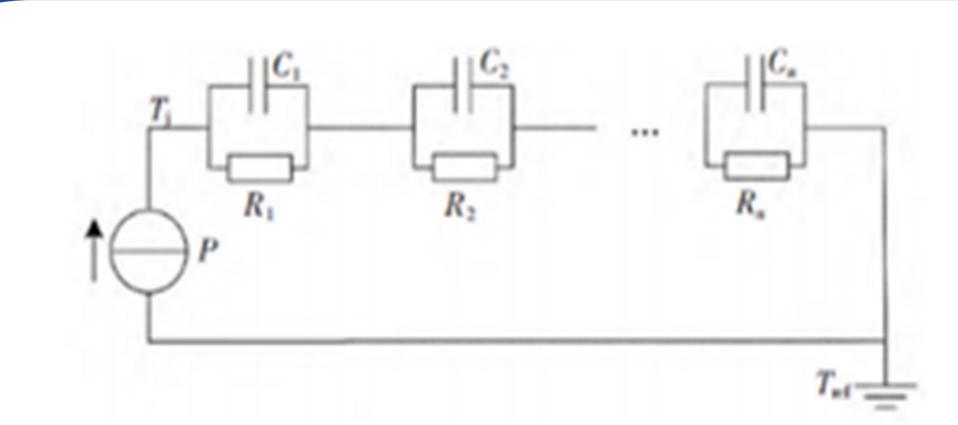

**Fig. 2** Equivalent heat path diagram of Foster thermal network

$$T(t) = P \sum_{i=1}^{n} R_{th,i} (1 - e^{\frac{-\iota}{\tau_i}})$$

(a)

$Z_{th}(t) = \sum_{i=1}^{n} R_{th,i} (1 - e^{\frac{\tau}{\tau_i}})$  (b)

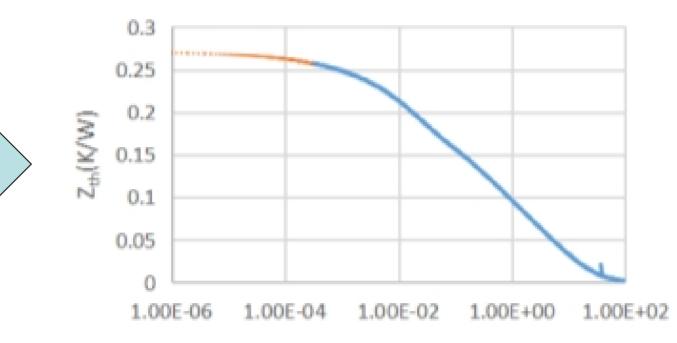

The transient behavior of heat source shown by (a) can be recognized as the response to the device dissipation power stimulation of the equivalent heat path which is shown in Fig. 2 and the transient resistance of corresponding thermal network can be

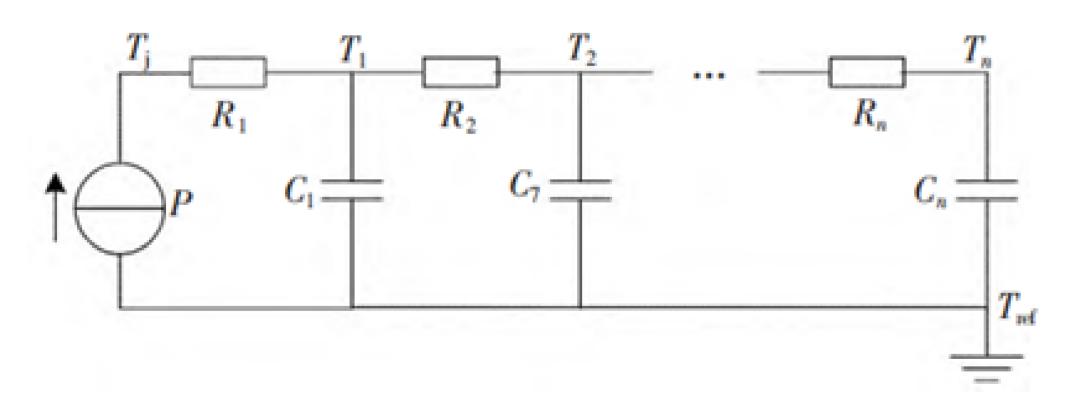

the thermoelectric comparison theory, current In corresponds to heat flow in a thermal network, voltage difference is analogous to temperature difference, resistance corresponds to thermal resistance, and capacitance corresponds to thermal capacity. The heat dissipation pattern of most power electronic devices with single-sided heat dissipation can be characterized by the Cauer model, whose thermal network model can be represented by Fig.1.

**Fig 1.** Equivalent thermal circuit diagram of Cauer thermal network

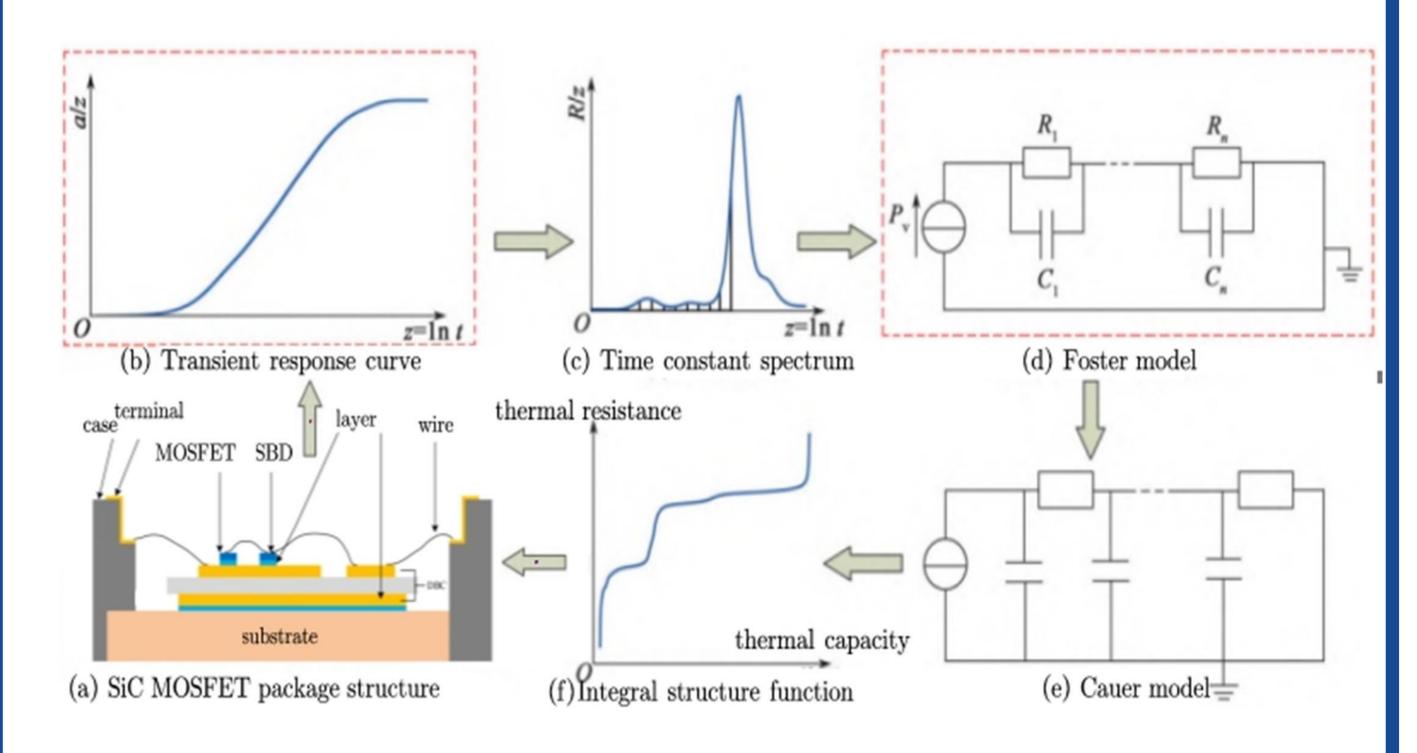

expressed by (b). Fig 3. shows the main steps to analysis the thermal network model of device using the structure function method.

Fig 3. Analysis of thermal network models of device using the structure function method

Now, we can use MATLAB to conduct Foster thermal network iteration fitting, which uses the built-in nonlinear function — — Isqcurvefit to fit related parameters of Foster thermal network. The function's essential principle is least square method.

## **3. Device Thermal Network Parameter Extraction Algorithm**

For the difficulty of calculating the parameters of each layer of the Cauer network directly, it is necessary to obtain the Foster thermal network model shown in Fig.2 from the device cooling curve first

Table1

WAB300M12BM3

Foster

Model

Thermal Network Parameters

| - | i                    | 1       | 2       | 3        | 4       | 5       | 6       | 7        |

|---|----------------------|---------|---------|----------|---------|---------|---------|----------|

| - | r <sub>i</sub> (K/W) | 0.05904 | 0.04503 | 0.01323  | 0.05483 | 0.03678 | 0.06175 | 0.01972  |

| _ | c <sub>i</sub> (J/K) | 62.725  | 397.910 | 0.005989 | 0.29207 | 2.75098 | 12.6643 | 0.078899 |

#### **b b c i m**

# An Automatic Optimization Algorithm of SiC MOSFET Power Cycling Test parameters Based on the Device Thermal Networks

The whole process includes four steps: measuring the thermal transient response to the cooling curve, using the  $\sqrt{t}$  method to fit the front end of the cooling curve, the use of 1sqcurvefit function to fit the Foster thermal network, the Foster and Cauer network model conversion.

# **Fig.4.** Analysis of thermal network models of device using the 1sqcurvefit function

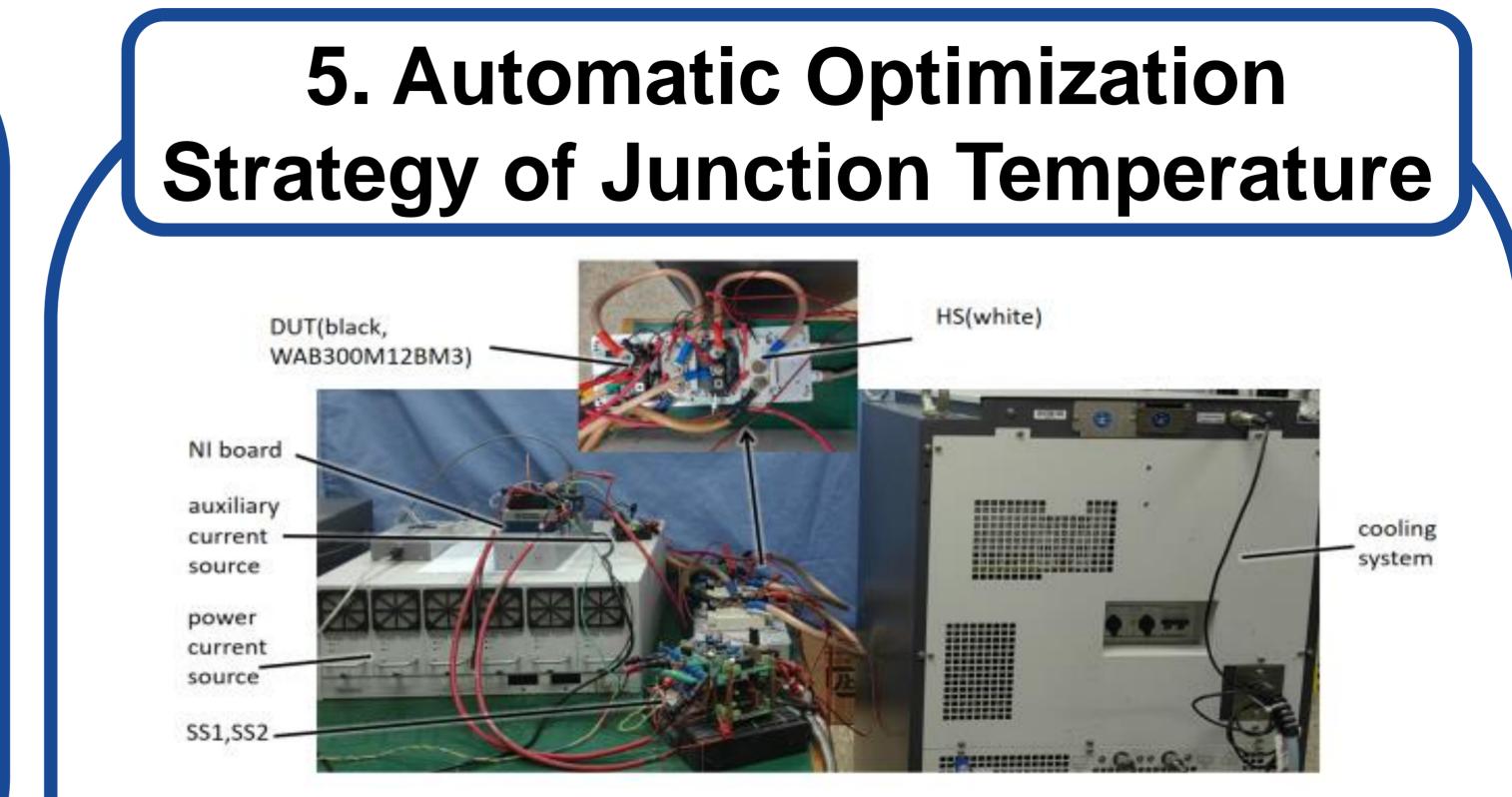

### Fig.5 Experimental system

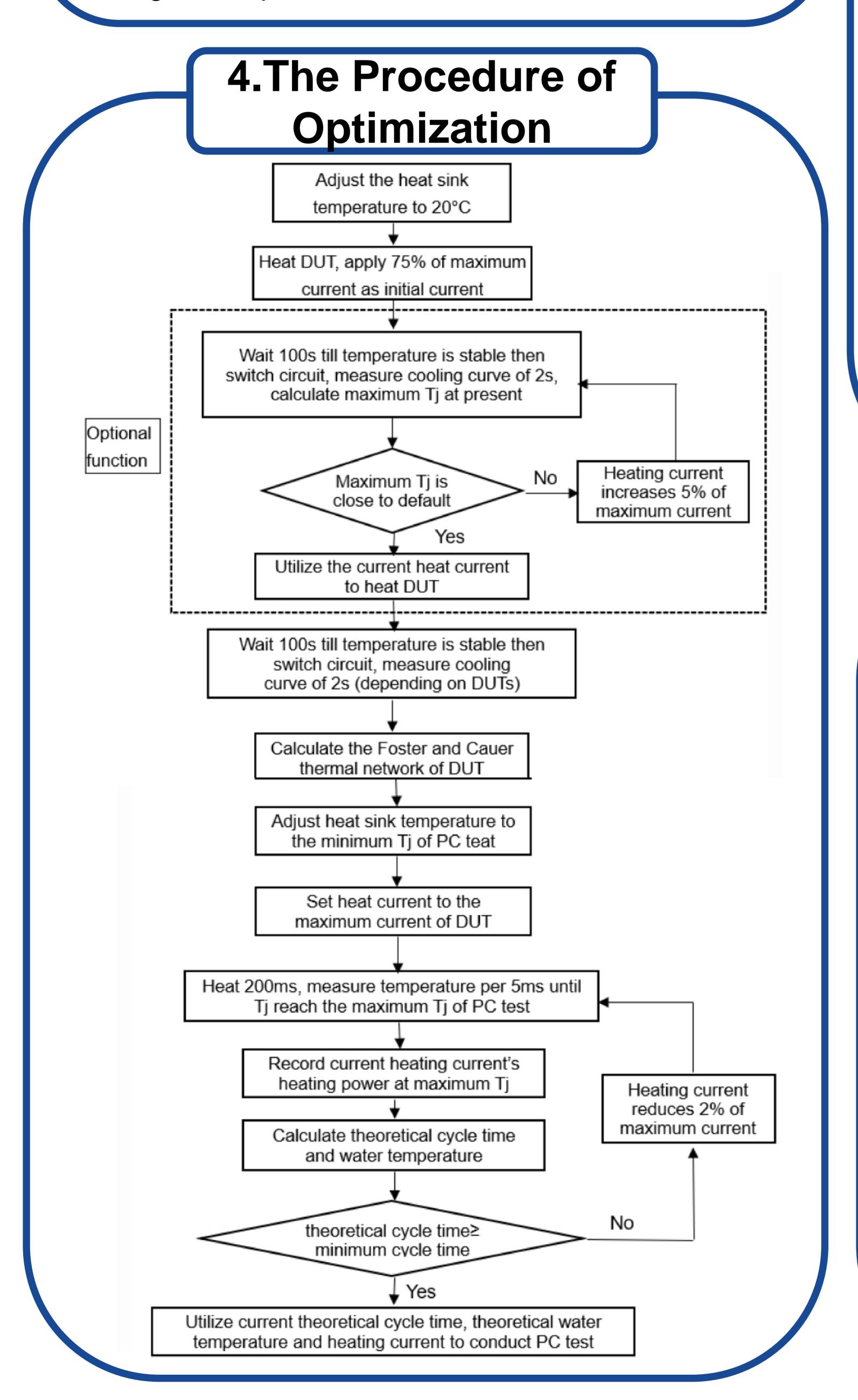

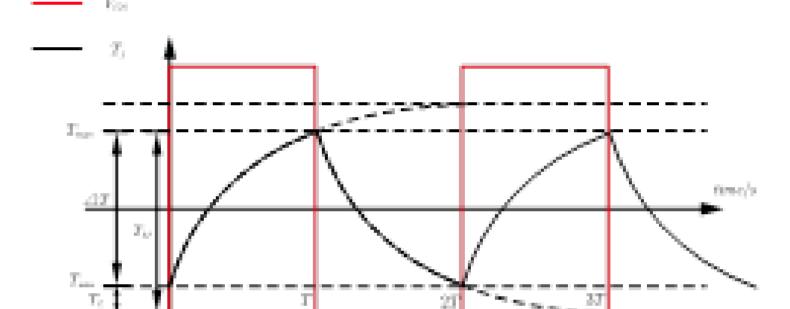

The most important two parameters of PC tests are  $T_{j\_max}$  and difference of  $T_j (\Delta T_j)$ . This paper realized adjusting parameters to meet requirements of tests  $T_j$  by algorithms.Fig.5 shows the experimental system and the fluctuation of device's  $T_j$  in PC test is shown in Fig.6.

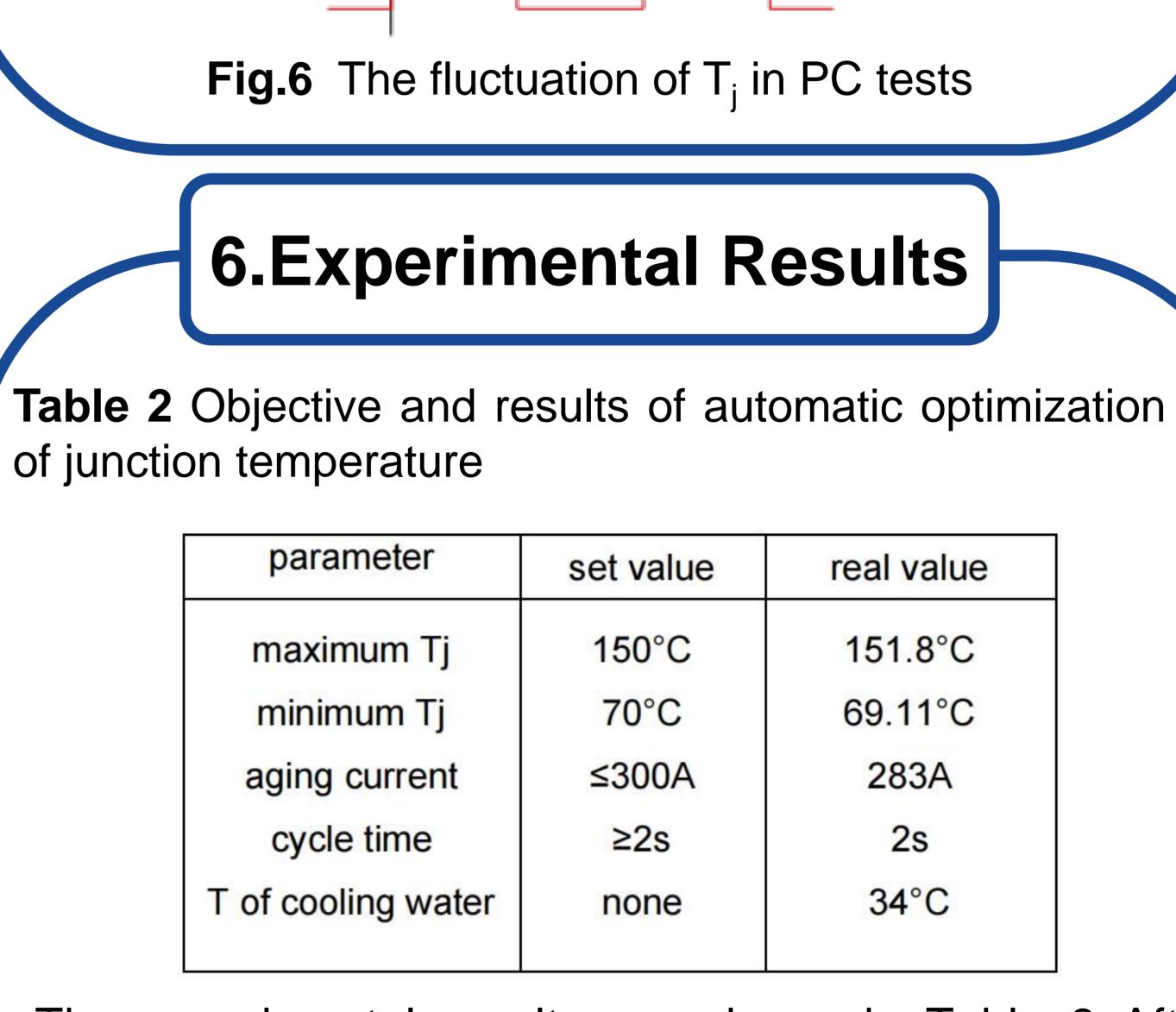

The experimental results are shown in Table 2. After setting a series of preset conditions, the system automatically completes the calculation, and the error of Tj is within  $\pm 2^{\circ}$ C. After removing the stabilization process after the temperature change of the heat sink, the automatic optimization and adjustment process of the junction temperature only takes 5 minutes. Experimental results show that the algorithm has good results and the accuracy meets the requirements of PC testing.