#### **b b c i m**

# **Research on Electrical Characteristics of 1200V SiC Trench MOSFET with Periodic Arrangement of 3D P-shield Structure**

Guan Song, Yafei Wang, Yao Yao, Qiming He, Qijun Liu, Xin Yuan, Chengzhan Li, Qiang Xiao, Haihui Luo

Zhuzhou CRRC Times Semiconductor Co., LTD, Tianxin High-tech Park, Shifeng District, Zhuzhou, Hunan, P.R.China

### Introduction

Compared to planar MOSFETs, trench MOSFETs can reduce cell-pitch and enhance current density, earning them increasing favor. This paper developed a 1200V trench MOSFET featuring a periodic P-type shielding structure in three dimensions(3D P-shield), exhibits outstanding current capacity robustness.

## **Structure Design**

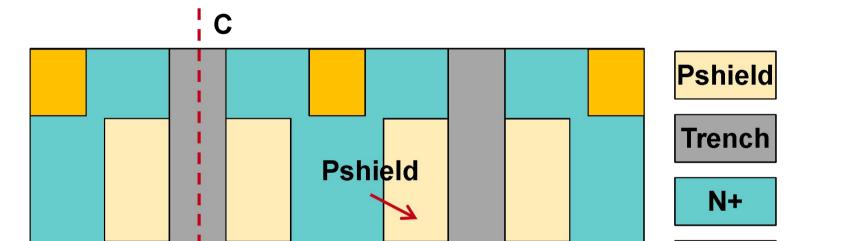

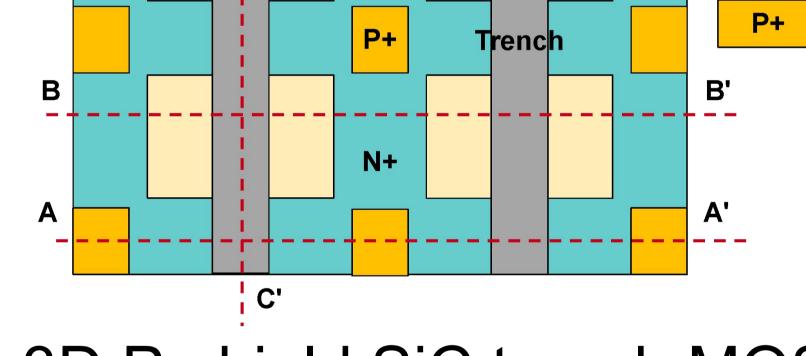

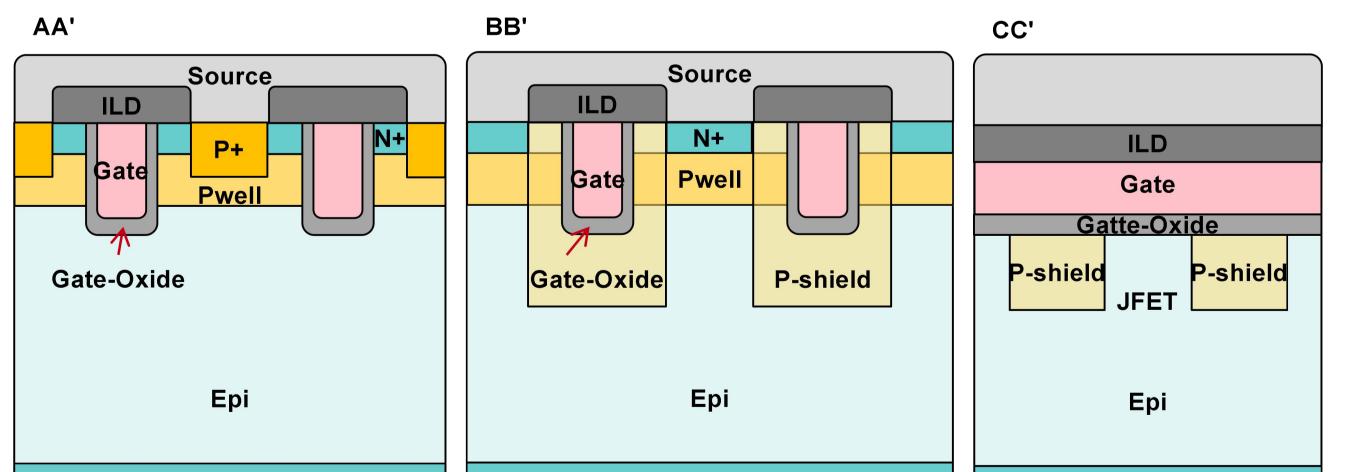

The top and cross-sectional views of the 3D P-shield SiC Trench MOSFET are shown in Fig1,2.

## **Critical process**

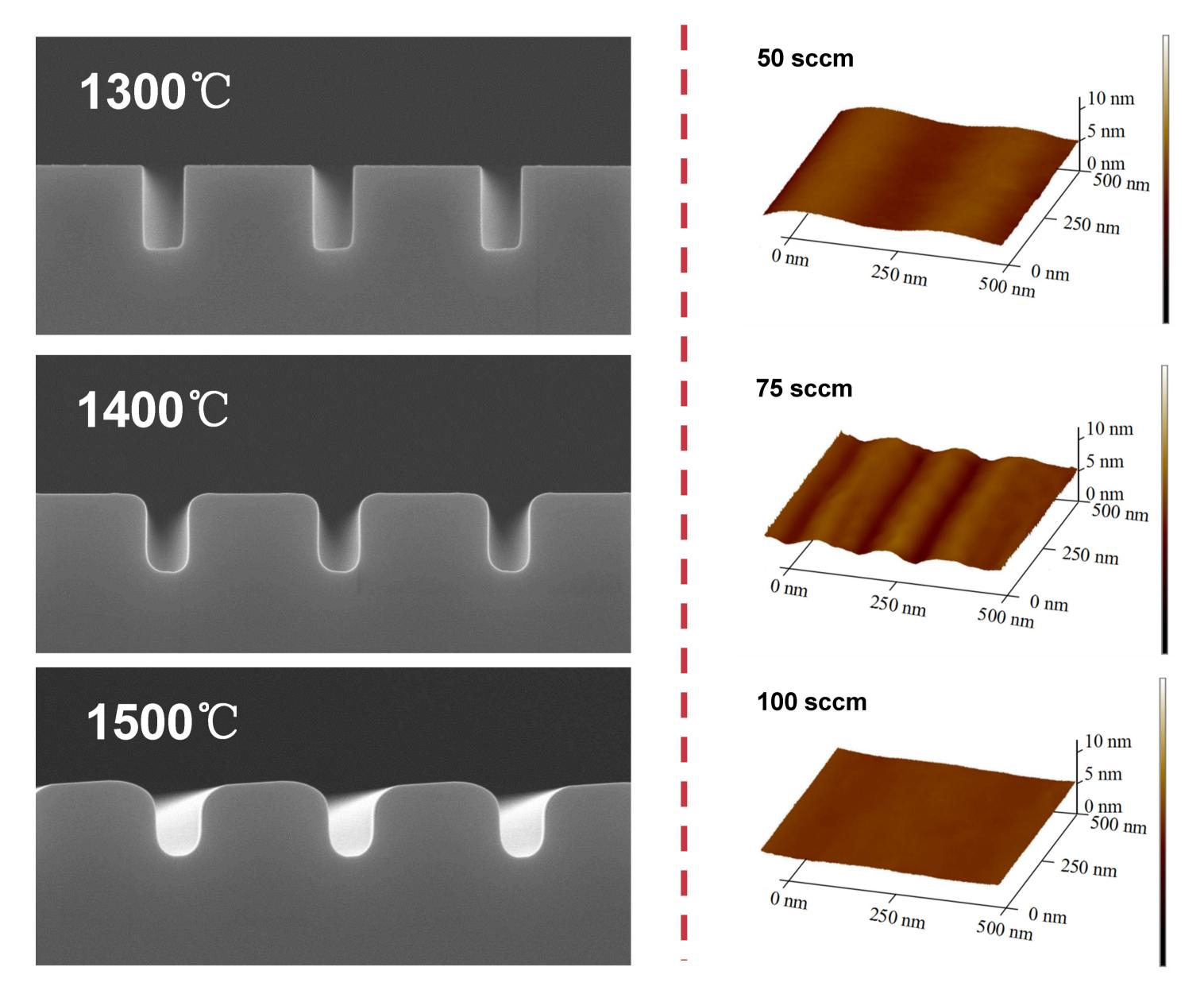

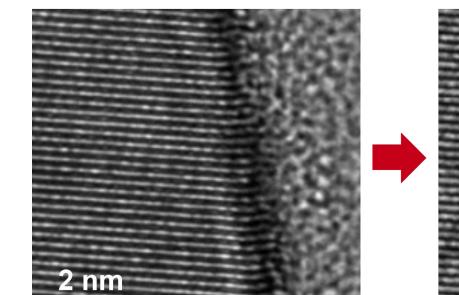

A roughness of 0.11 nm on the trench sidewalls was achieved, mitigating the scattering effects of surface roughness.

Fig.1 3D P-shield SiC trench MOSFET

When the device is turned on, channels form on both sides of the trench in region AA', with the N+ area supplying electrons for conduction.

Fig.3 Trench appearance after different H<sub>2</sub>

Fig.4 Trench side-wall roughness under

| ≈ Substrate ≈ | ≈ Substrate ≈ | ≈ Substrate ≈ |

|---------------|---------------|---------------|

| Drain         | Drain         | Drain         |

# Fig.2 Cross section of the 3D P-shield SiC trench MOSFET

In the reverse bias state, the P-shield structure depletes within the epitaxial layer, reducing electric field stress concentration at the trench bottom's gate oxide layer

### annealing temperature

### different H<sub>2</sub> flow rate

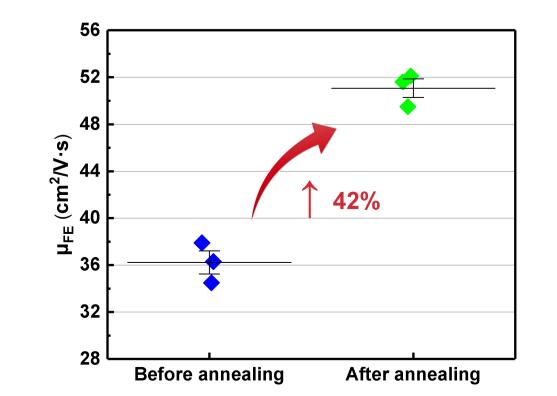

**Fig.5** Effect of lattice repair after hightemperature annealing **Fig.6** Field-effect mobility before and after process optimization

# **Research on Electrical Characteristics of 1200V SiC Trench MOSFET** with Periodic Arrangement of 3D P-shield Structure

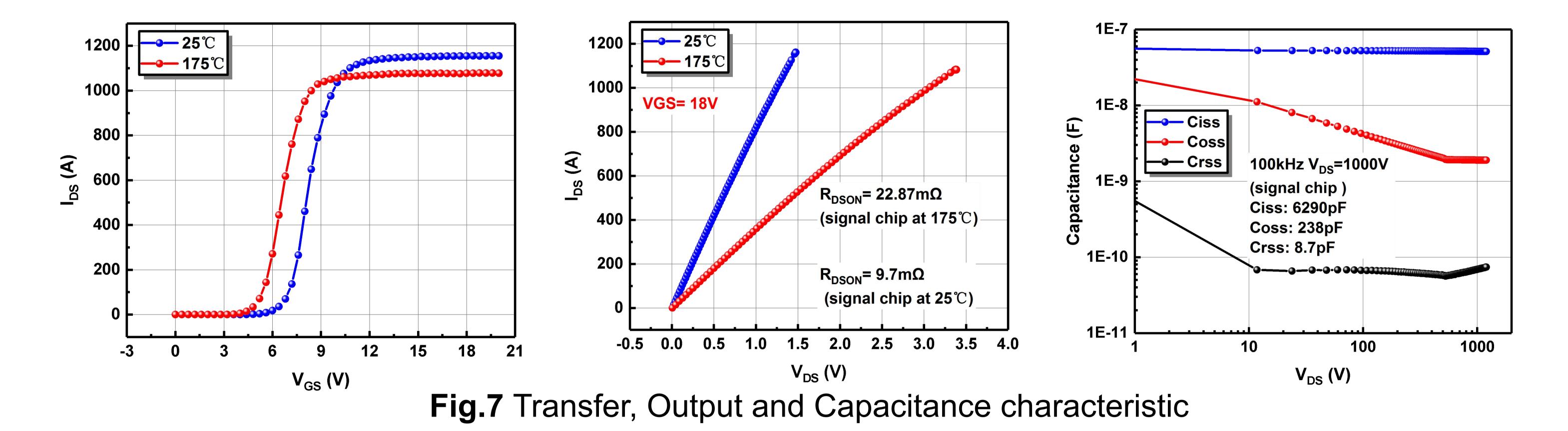

**Electrical Characteristics**

### Chip size 5mm\*5mm, L5 series format (8 chips in parallel)

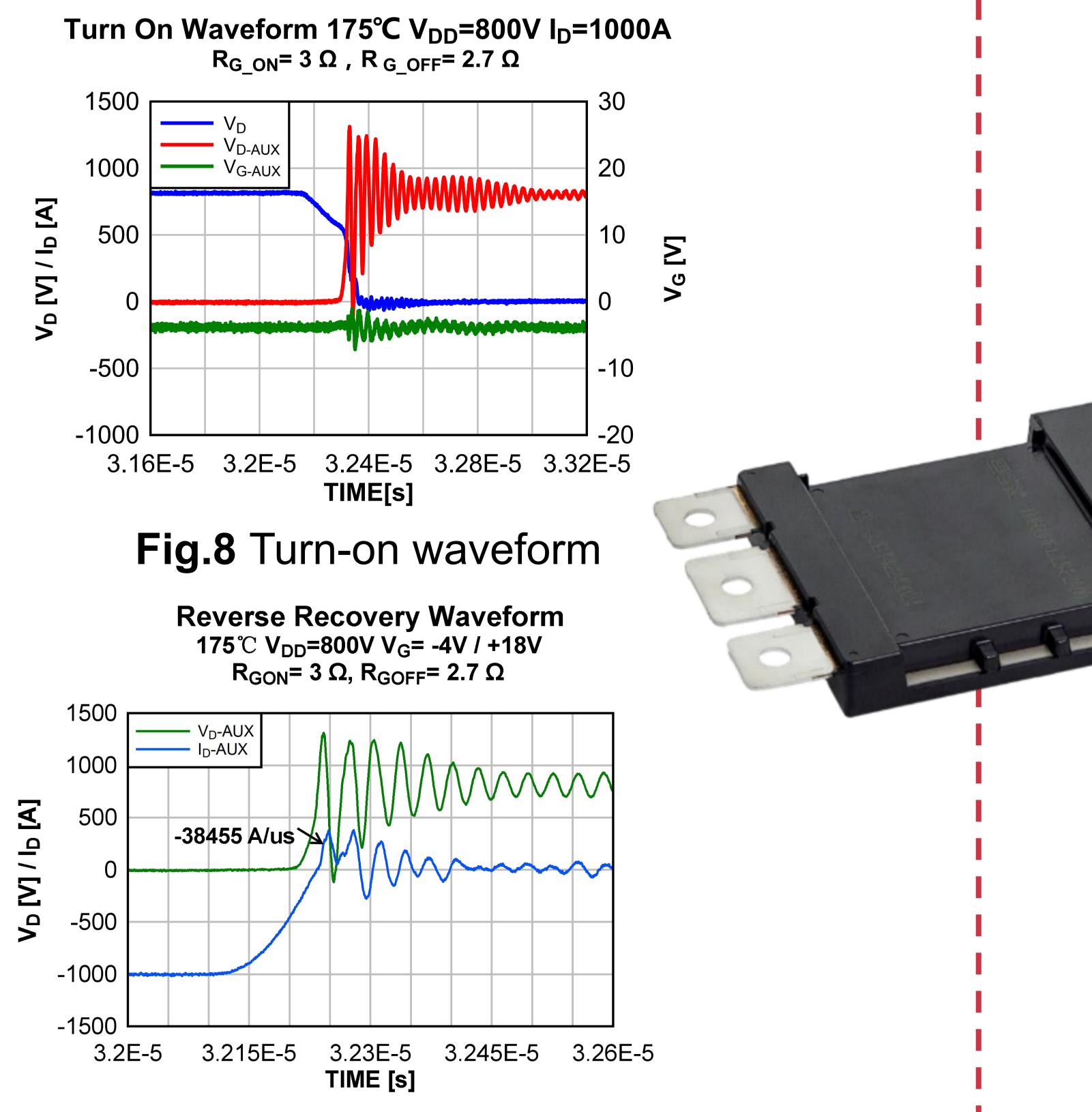

The Vrm during turn-on processis higher due to the rapid carrier extraction in the body region during the reverse recovery process, leading to a large dirr/dt and severe voltage overshoot, which constrains further increases in turn-on speed.

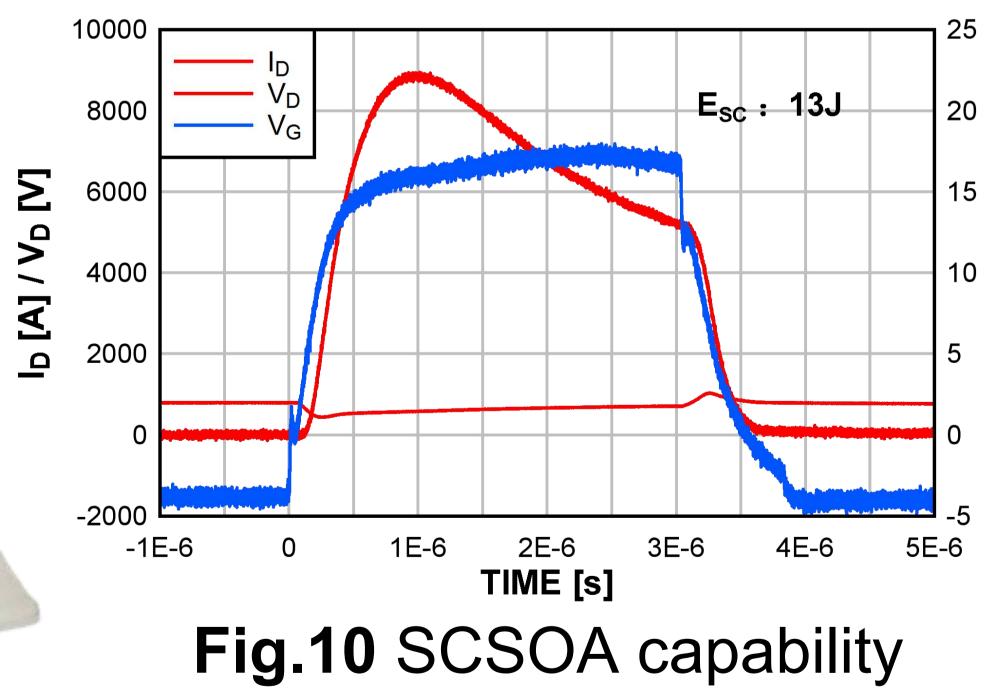

The 3D P-shield structure reduces the device's saturation current, thanks to its high doping concentration and junction depth, achieving a short-circuit withstand of 3µs and a short-circuit energy (ESC) of 13J

Short Circuit Waveform 175<sup>°</sup>C V<sub>DD</sub>=800V 175℃ V<sub>DD</sub>=800V, V<sub>GS</sub>= -4V /+18V  $R_{GON}$ = 3  $\Omega$ ,  $R_{GOFF}$ = 2.7  $\Omega$

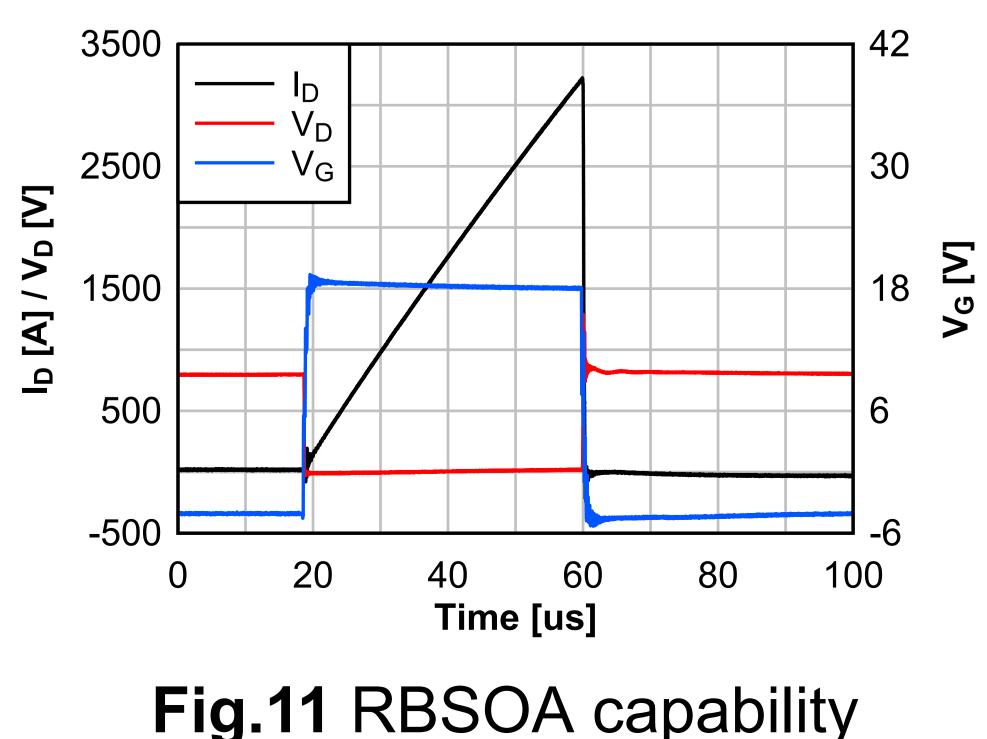

**RBSOA** waveform  $175^{\circ}CV_{GS} = -4V / +18V$  $R_{GON}$ = 3 Ω,  $R_{GOFF}$ = 2.7 Ω

Fig.9 Reverse recovery waveform